ホーム > 特集

特集

暗号ハードウェアの耐タンパ性評価

はじめに

サイバーフィジカルセキュリティ対策は我が国を挙げて取り組んでいる重要な政策の一つであり、システムの規模に関わらずサイバー攻撃の脅威があることを前提として、サプライチェーン全体にわたって基礎的なセキュリティ対策を講じることが求められている。産業分野をはじめとして広く導入されているIoTデバイスでは、厳しい動作性能や限られた計算資源の制約下でセキュリティ対策を実装する必要がある。

このような背景から、低遅延動作や低エネルギー動作といった特性をもつ暗号技術として軽量暗号[1, 2]が提案されており、いくつかの暗号方式が国際標準規格として採用されるなど注目されている。一方で、軽量暗号は計算量的困難性に基づいて安全性が担保されているものの、暗号実装時に生じる物理的な漏洩情報を用いるサイドチャネル攻撃に脆弱であることが指摘されている[3]。従って、暗号ハードウェアのセキュア実装を実現するためには、サイドチャネル攻撃の脅威の検討およびその対策手法の確立が重要である。

サイドチャネル攻撃

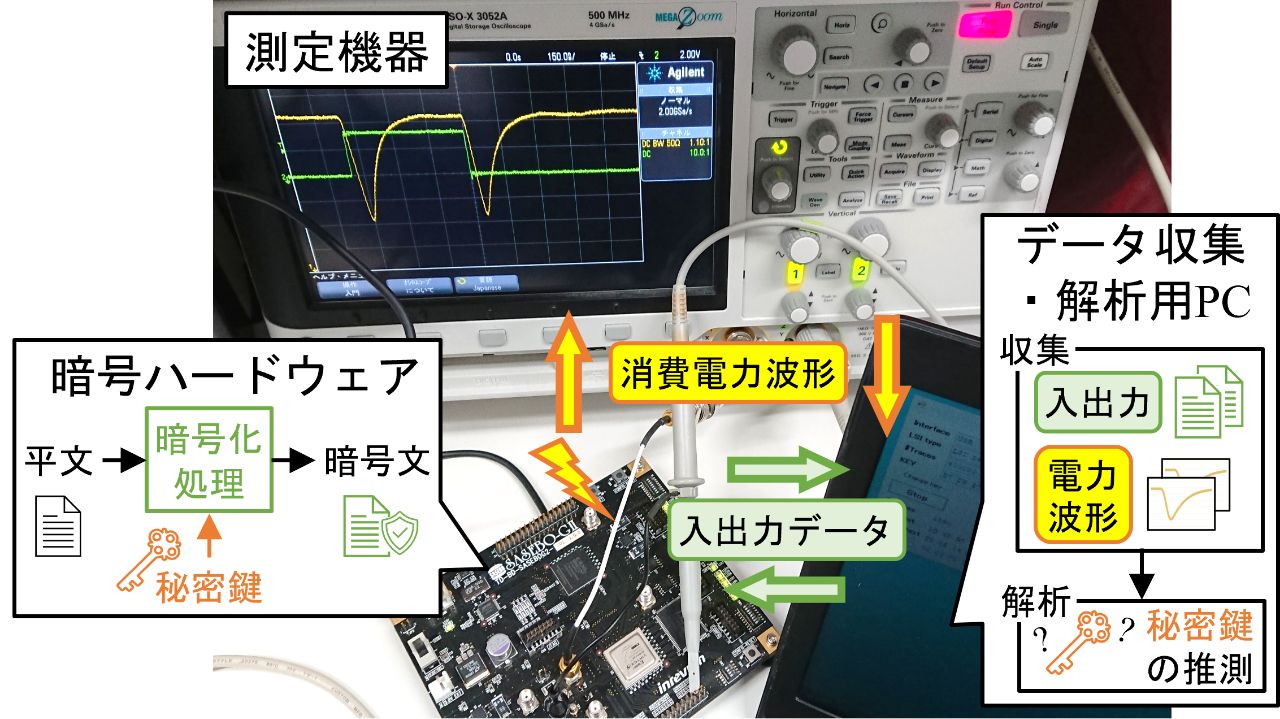

サイドチャネル攻撃[3]は、図1に示すように、既知の入出力値に加え、暗号ハードウェアから漏洩するサイドチャネル情報を大量に収集することで、秘匿情報を統計的に推測する攻撃である。サイドチャネル情報には、消費電力や漏洩電磁波、クロックグリッチの注入によって生じる故障入り暗号文などが用いられる。本稿では、消費電力を用いた手法である電力解析攻撃に着目して説明する。

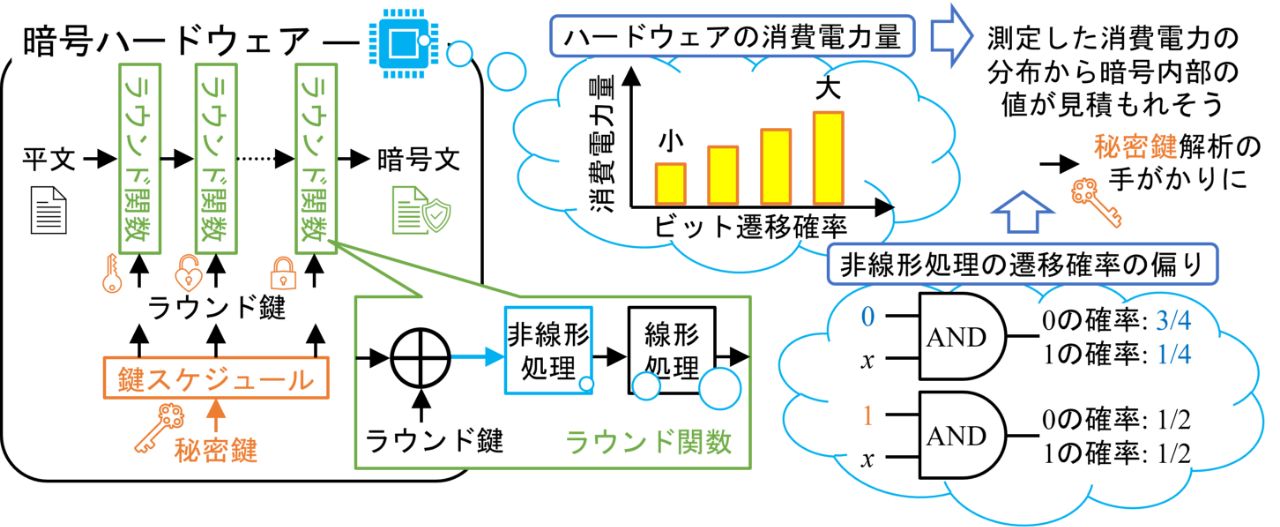

電力解析攻撃は、暗号ハードウェアの消費電力と、暗号演算中の値(暗号中間値)との間の相関を利用することで、暗号の秘匿情報である秘密鍵を解析する手法である(図2)。暗号ハードウェアデバイスの消費電力量は、暗号中間値の遷移確率に依存し、0と1のスイッチング回数が多いほど電力が大きくなる。また、暗号方式は、暗号中間値の0と1の割合が約1/2になるように、値を撹拌することで安全性を確保するように設計されている。一方で、非線形処理の入力値に着目すると、その値が0か1かによって遷移確率に偏りが生じる。そこで、これらの特性を利用し、大量の消費電力波形と既知の入出力情報を用いて統計的に内部の演算情報を推定することで、未知の秘密鍵の値を解析することができる。

サイドチャネル攻撃は、比較的安価な測定機器を用いて、対象の暗号ハードウェアを破壊することなく解析することができるため、脅威の大きい攻撃手法である。そのため、サイドチャネル攻撃に対する暗号ハードウェアの安全性(耐タンパ性)を評価する手法が国際標準化されている。また、次世代標準暗号を選出するためのコンペティションでは、暗号の構成要件としてサイドチャネルの対応が求められているなど、暗号ハードウェアにおいてサイドチャネル攻撃は重要な研究テーマである。

研究紹介

代表的な軽量暗号として、低遅延動作可能なPRINCE[1]および低エネルギー動作可能なMidori128[2]に対する耐タンパ性評価に関する研究[4]を紹介する。

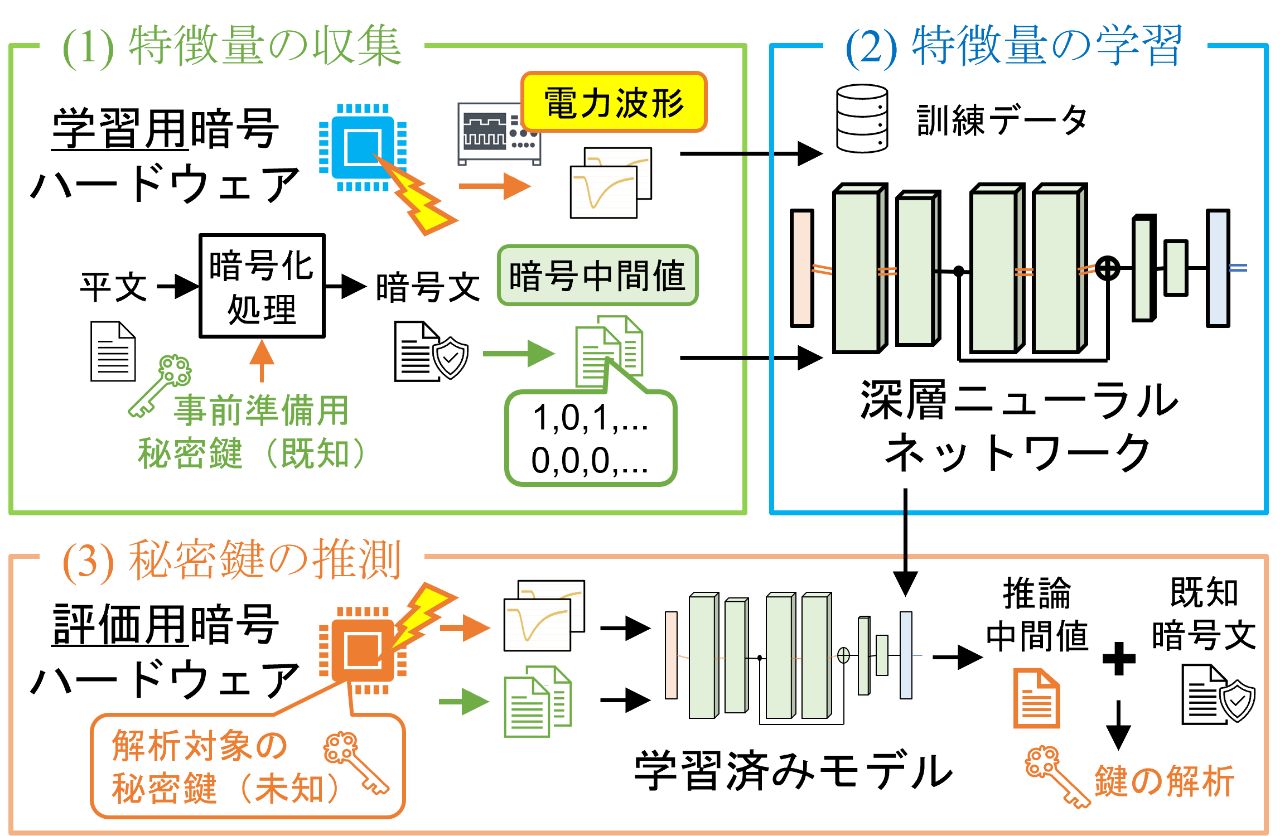

本研究では、軽量暗号の詳細な耐タンパ性を明らかにするために、従来の電力解析手法をベースとした新たな深層学習電力解析を提案している。提案評価手法は、図3に示すように、(1)特徴量の収集、(2)特徴量の学習、(3)秘密鍵の推測の3段階で構成される。まず(1)では、事前に用意した暗号ハードウェアを用いて、従来の解析手法と同様に消費電力波形と暗号中間値のデータを収集する。次に(2)では、深層学習モデルを用いてこれらのデータ間の相関関係を学習する。深層学習モデルには、ResNetをベースとしたネットワークを採用し、消費電力波形に含まれる軽量暗号の微細な特徴量を抽出し学習する。最後に(3)では、未知の秘密鍵が組み込まれた暗号ハードウェアを対象に、消費電力波形を学習済みモデルに入力し、推論の結果得られた中間値と既知の入出力値から、最も尤度の高い秘密鍵を推測する。このように提案手法では、事前に暗号ハードウェアの情報をプロファイリングしておくことで、解析に必要な使用波形数を削減し、電力測定時間および解析時間を短縮できるため、より広範な攻撃シナリオを想定した評価が可能となる。

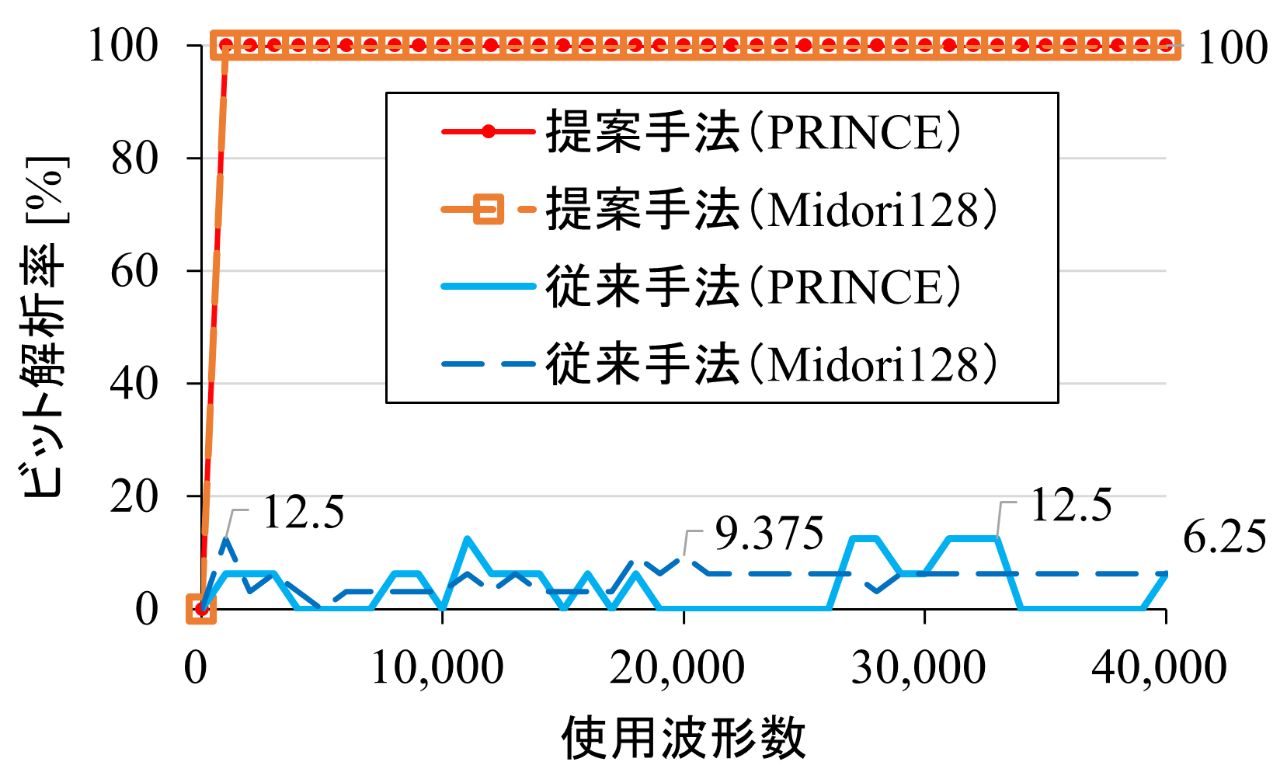

提案評価手法の有効性を、Field-Programmable Gate Array(FPGA)が搭載された評価用ボードを含む図1の実験環境を用いて検証した。図4は、提案手法である深層学習電力解析と従来の電力解析手法[3]の比較結果を示す。横軸は収集したデータ数、縦軸は秘密鍵ビット長に対する解析成功ビット数の割合を示す。従来手法が最大12.5%の正解ビット解析率であるのに対し、提案手法はPRINCEおよびMidori128ともにすべてのビットを解析しており、提案評価手法を用いて評価対象の暗号ハードウェア(PRINCEおよびMidori128)の耐タンパ性が十分でないことを明らかにした。そのため、実装オーバーヘッドの増加によって軽量暗号の特性が損なわれる可能性を考慮しつつ、高次のマスキング対策などの堅牢な対策手法の適用が重要であると考えられる。

まとめ

本稿ではサイドチャネル攻撃の概要と研究内容について紹介した。今後の課題として、セキュリティとフィージビリティを両立可能な、暗号ハードウェアのセキュア実装手法の検討が挙げられる。

参考文献

1. J. Borghoff, A. Canteaut, T. Güneysu, E. B. Kavum, M. Knežević, L. R. Knudsen, G. Leander, V. Nikov, C. Paar, C. Rechberger, P. Rombouts, S. S. Thomsen, and T. Yalçin, “PRINCE - A Low-latency Block Cipher for Pervasive Computing Applications,” Proc. of the 18th Annual Int. Conf. on the Theory and Application of Cryptology and Information Security (ASIACRYPT 2012), LNCS vol. 7658, pp. 208–225, Springer, Dec. 2012.

2. S. Banik, A. Bogdanov, T. Isobe, K. Shibutani, H. Hiwatari, T. Akishita, and F. Regazzoni, “Midori: A Block Cipher for Low Energy,” Proc. of the 21st Annual Int. Conf. on the Theory and Application of Cryptology and Information Security (ASIACRYPT 2015), LNCS, vol. 9453, pp. 411‒436, Springer, Dec. 2015.

3. E. Brier, C. Clavier, and F. Olivier, “Correlation Power Analysis with a Leakage Model,” Proc. of the 6th Int. Workshop on Cryptographic Hardware and Embedded Systems (CHES 2004), LNCS, vol. 3156, pp. 16–29, Springer, Aug. 2004.

4. 竹本修、池崎良哉、野崎佑典、吉川雅弥、“セキュアブロック暗号に対する網羅的な深層学習電力解析とその評価、”電気学会論文誌C、vol. 144、no. 1、pp. 7–14、2024年1月

https://doi.org/10.1541/ieejeiss.144.7